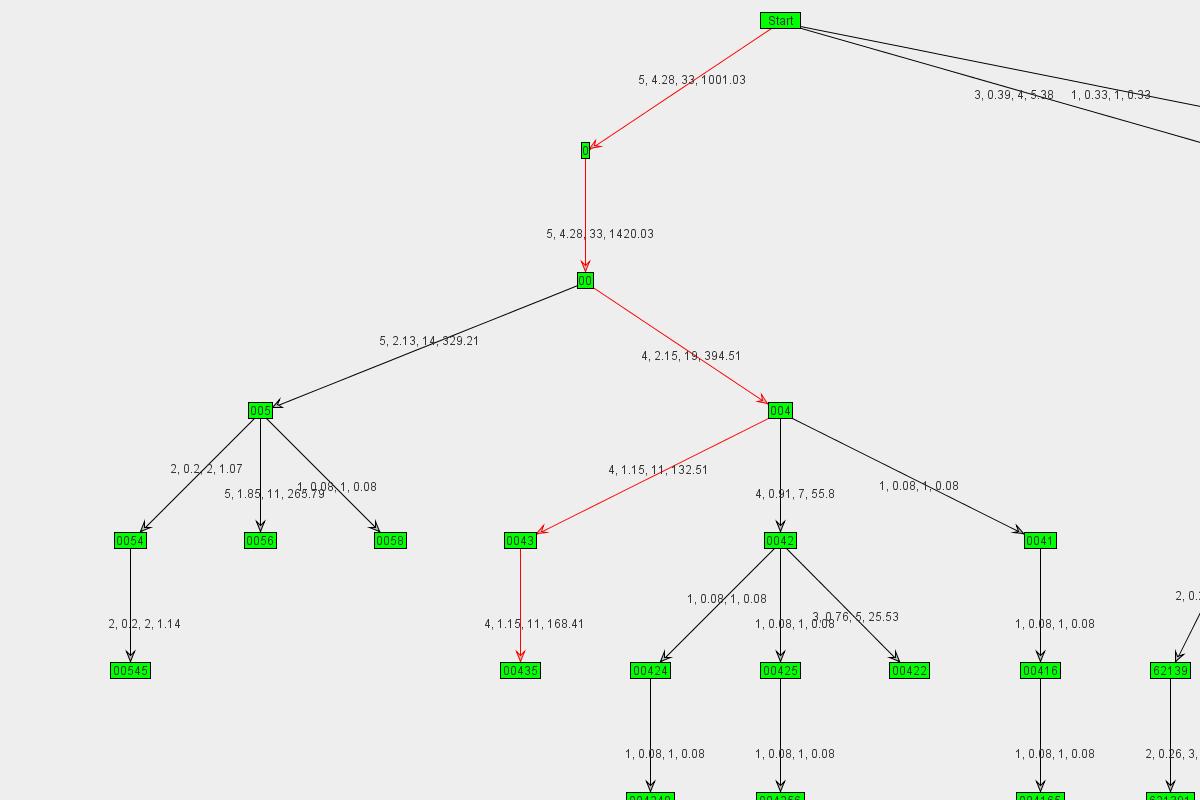

Automatically assigned DDC number: 00435

Manually assigned DDC number: 00435

Number of references: 4

Title: Comparing Static And Dynamic Code Scheduling for Multiple-Instruction-Issue Processors

Author:

Author:

Author:

Author:

Subject: Pohua P. Chang,William Y. Chen,Scott A. Mahlke,Wen-mei W. Hwu Comparing Static And Dynamic Code Scheduling for Multiple-Instruction-Issue Processors

Description: This paper examines two alternative approaches to supporting code scheduling for multiple-instruction-issue processors. One is to provide a set of non-trapping instructions so that the compiler can perform aggressive static code scheduling. The application of this approach to existing commercial architectures typically requires extending the instruction set. The other approach is to support out-of-order execution in the microarchitecture so that the hardware can perform aggressive dynamic code scheduling. This approach usually does not require modifying the instruction set but requires complex hardware support. In this paper, we analyze the performance of the two alternative approaches using a set of important nonnumerical C benchmark programs. A distinguishing feature of the experiment is that the code for the dynamic approach has been optimized and scheduled as much as allowed by the architecture. The hardware is only responsible for the additional reordering that cannot be performed...

Contributor: The Pennsylvania State University CiteSeer Archives

Publisher: unknown

Date: 1992-06-02

Pubyear: 1991

Format: ps

Identifier: http://citeseer.ist.psu.edu/148295.html

Source: ftp://ftp.crhc.uiuc.edu/pub/IMPACT/conference/micro-91-dynamic.ps

Language: en

Relation:

Relation:

Relation:

Relation:

Rights: unrestricted

<?xml version="1.0" encoding="UTF-8"?>

<references_metadata>

<rec ID="/259386.html" Type="article" CiteSeer_Book="IEEE Transactions on Computers" CiteSeer_Volume="41" Title="Efficient Instruction Sequencing with Inline Target Insertion,">

<identifier Org="ISBN:013518200X" Paper_ID="/259386.html" Extracted="013518200X" DDC="004.2/2" Normalized_DDC="00422" Normalized_Weight="0.2" />

<identifier Org="ISBN:0780399757" Paper_ID="/259386.html" Extracted="0780399757" />

<identifier Org="ISBN:0792393678" Paper_ID="/259386.html" Extracted="0792393678" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.2" />

<identifier Org="ISBN:0818652802" Paper_ID="/259386.html" Extracted="0818652802" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.2" />

<identifier Org="ISBN:0897913949" Paper_ID="/259386.html" Extracted="0897913949" DDC="004.2/2" Normalized_DDC="00422" Normalized_Weight="0.2" />

<identifier Org="ISBN:0897914600" Paper_ID="/259386.html" Extracted="0897914600" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.2" />

</rec>

<rec ID="/332200.html" Type="inproceedings" CiteSeer_Book="Proceedings of the 3rd International Conference on Architectural Support for Programming Languages and Operating System ASPLOS" CiteSeer_Volume="" Title="Available Instruction-Level Parallelism for Superscalar and Superpipelined Machines,">

<identifier Org="ISBN:0070570647" Paper_ID="/332200.html" Extracted="0070570647" DDC="621.39/16" Normalized_DDC="6213916" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0792375866" Paper_ID="/332200.html" Extracted="0792375866" DDC="621.39/16" Normalized_DDC="6213916" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0792384636" Paper_ID="/332200.html" Extracted="0792384636" DDC="004.165" Normalized_DDC="004165" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0792393678" Paper_ID="/332200.html" Extracted="0792393678" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0818631759" Paper_ID="/332200.html" Extracted="0818631759" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0818642300" Paper_ID="/332200.html" Extracted="0818642300" />

<identifier Org="ISBN:0818670940" Paper_ID="/332200.html" Extracted="0818670940" DDC="004.2/4/011" Normalized_DDC="00424011" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0849326184" Paper_ID="/332200.html" Extracted="0849326184" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:0867204745" Paper_ID="/332200.html" Extracted="0867204745" DDC="004.25/6" Normalized_DDC="004256" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:3540423001" Paper_ID="/332200.html" Extracted="3540423001" DDC="005.8" Normalized_DDC="0058" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:3540555994" Paper_ID="/332200.html" Extracted="3540555994" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:3540578773" Paper_ID="/332200.html" Extracted="3540578773" DDC="005.4/5" Normalized_DDC="00545" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:354060054X" Paper_ID="/332200.html" Extracted="354060054X" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.07692307692307693" />

<identifier Org="ISBN:3540662286" Paper_ID="/332200.html" Extracted="3540662286" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.07692307692307693" />

</rec>

<rec ID="/518348.html" Type="inproceedings" CiteSeer_Book="Proceedings of the 3rd International Conference on Architectural Support for Programming Languages and Operating System ASPLOS" CiteSeer_Volume="" Title="Limits on Multiple Instruction Issue,">

<identifier Org="ISBN:0070570647" Paper_ID="/518348.html" Extracted="0070570647" DDC="621.39/16" Normalized_DDC="6213916" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:0780335589" Paper_ID="/518348.html" Extracted="0780335589" />

<identifier Org="ISBN:0818620471" Paper_ID="/518348.html" Extracted="0818620471" />

<identifier Org="ISBN:081862079X" Paper_ID="/518348.html" Extracted="081862079X" />

<identifier Org="ISBN:0818631759" Paper_ID="/518348.html" Extracted="0818631759" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:0818642300" Paper_ID="/518348.html" Extracted="0818642300" />

<identifier Org="ISBN:0818652802" Paper_ID="/518348.html" Extracted="0818652802" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:0818679778" Paper_ID="/518348.html" Extracted="0818679778" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:0849307805" Paper_ID="/518348.html" Extracted="0849307805" />

<identifier Org="ISBN:0849326184" Paper_ID="/518348.html" Extracted="0849326184" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:0879426780" Paper_ID="/518348.html" Extracted="0879426780" />

<identifier Org="ISBN:1558605967" Paper_ID="/518348.html" Extracted="1558605967" DDC="004.2/2" Normalized_DDC="00422" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:3540616276" Paper_ID="/518348.html" Extracted="3540616276" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:3540662286" Paper_ID="/518348.html" Extracted="3540662286" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.1111111111111111" />

<identifier Org="ISBN:3540679561" Paper_ID="/518348.html" Extracted="3540679561" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.1111111111111111" />

</rec>

<rec ID="/413787.html" Type="inproceedings" CiteSeer_Book="Proceedings of the 17th Annual Symposium on Computer Architecture" CiteSeer_Volume="" Title="Boosting beyond static scheduling in a superscalar processor,">

<identifier Org="ISBN:0769505740" Paper_ID="/413787.html" Extracted="0769505740" />

<identifier Org="ISBN:0780335589" Paper_ID="/413787.html" Extracted="0780335589" />

<identifier Org="ISBN:0792393678" Paper_ID="/413787.html" Extracted="0792393678" DDC="004/.35" Normalized_DDC="00435" Normalized_Weight="0.125" />

<identifier Org="ISBN:0818620471" Paper_ID="/413787.html" Extracted="0818620471" />

<identifier Org="ISBN:0818631759" Paper_ID="/413787.html" Extracted="0818631759" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.125" />

<identifier Org="ISBN:0818642300" Paper_ID="/413787.html" Extracted="0818642300" />

<identifier Org="ISBN:0818652802" Paper_ID="/413787.html" Extracted="0818652802" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.125" />

<identifier Org="ISBN:0818679778" Paper_ID="/413787.html" Extracted="0818679778" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.125" />

<identifier Org="ISBN:0897915348" Paper_ID="/413787.html" Extracted="0897915348" DDC="004.2/2" Normalized_DDC="00422" Normalized_Weight="0.125" />

<identifier Org="ISBN:0897916980" Paper_ID="/413787.html" Extracted="0897916980" DDC="621.38195205" Normalized_DDC="62138195205" Normalized_Weight="0.125" />

<identifier Org="ISBN:1581138040" Paper_ID="/413787.html" Extracted="1581138040" DDC="004.2/2" Normalized_DDC="00422" Normalized_Weight="0.125" />

<identifier Org="ISBN:3540578773" Paper_ID="/413787.html" Extracted="3540578773" DDC="005.4/5" Normalized_DDC="00545" Normalized_Weight="0.125" />

</rec>

<rec ID="SELF" Type="SELF" CiteSeer_Book="SELF" CiteSeer_Volume="SELF" Title="Comparing Static And Dynamic Code Scheduling for Multiple-Instruction-Issue Processors">

<identifier Org="ISBN:0818671262" Paper_ID="SELF" Extracted="0818671262" DDC="511.3" Normalized_DDC="5113" Normalized_Weight="0.3333333333333333" />

<identifier Org="ISBN:0818679778" Paper_ID="SELF" Extracted="0818679778" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.3333333333333333" />

<identifier Org="ISBN:0897914600" Paper_ID="SELF" Extracted="0897914600" DDC="005.6" Normalized_DDC="0056" Normalized_Weight="0.3333333333333333" />

</rec>

</references_metadata>